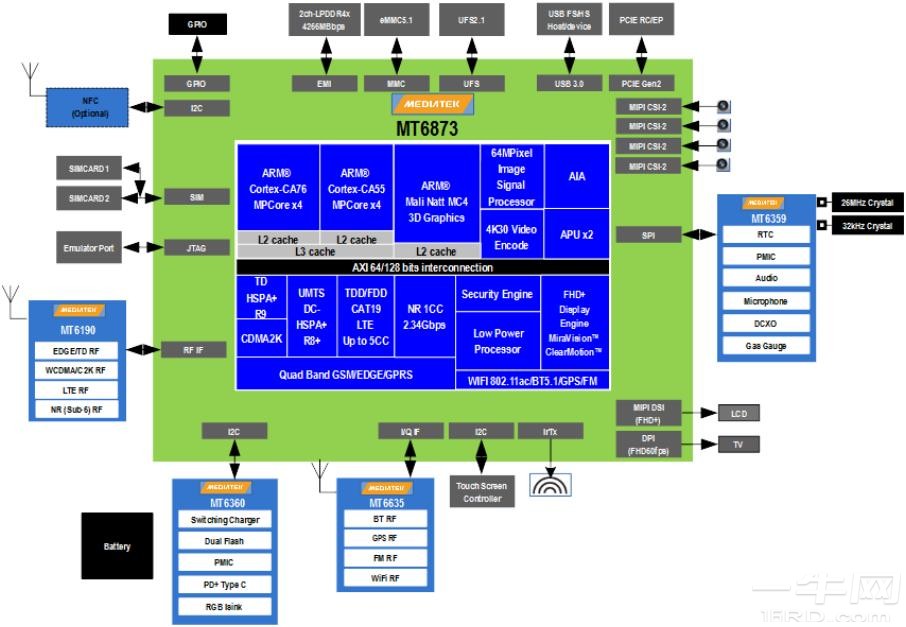

The MediaTek MT6873 5G processor integrates Bluetooth, FM, WLAN and GPS modules and is a highly integrated baseband platform that combines a modem and application processing subsystem to support LTE/LTE-A/NR and C2K smartphone applications. The chip integrates four ARM®Cortex-A76 cores operating at up to 2.0GHz, four ARM®Cortex-A55 cores operating at up to 2.0GHz, and powerful multi-standard video codecs. In addition, an extensive set of interfaces and interfaces for connecting peripheral cameras, touchscreen displays, and UFS/MMC/SD cards are included. The MT6873 processor is a multi-core ARM®Cortex-A76, ARM®Cortex-A55 equipped with a NEON engine that provides the processing power required to support the latest OpenOS and its demanding applications such as web browsing, email, GPS navigation, and gaming. Peculiarity:

1. AP MCU subsystem

- 4 ARM® 2.0 GHz Cortex-A76 cores, each with 64 KB L1 I-cache, 64 KB L1 Dcache, and 256 KB L2 cache

- 4 ARM® 2.0 GHz Cortex-A55 cores, each with 32 KB L1 I-cache, 32 KB L1 Dcache, and 128 KB L2 cache

- Shared 2 MB L3 cache

- NEON multimedia processing engine with SIMDv2/VFPv4 ISA support

- DVFS technology with adaptive operating voltage from 0.55V to 0.973V

2.MD MCU subsystem

- High-performance multi-core multi-threaded processor architecture

- High-performance AXI bus interface

- Generic DMA engine and dedicated DMA channel for peripheral data transfer

- Clock-gated power management

3. External memory interface

- LPDDR4X up to 16 GB (2 lanes, 16-bit data bus width)

- Data rates up to LPDDR4X-4266Mbps

- Self-refresh/partially self-refresh mode

- Low-power operation

- Programmable slew rate of memory controller I/O pads

- Dual column storage devices

- Advanced bandwidth quorum control

4. Peripherals

- USB one port with USB3.0 host/device mode or USB2.0 OTG mode

- eMMC5.1

- UFS 2.1

- 2 UARTs for debugging and application

- 8 SPI hosts for external devices

- 4 I2Cs/6 I3Cs to control peripherals such as CMOS image sensors, LCM or FM receiver modules

-Utmost. 4 PWM channels (depending on system configuration/IO usage)

- I2S for connecting an optional external high-end audio codec Peculiarity:

1. AP MCU subsystem

- 4 ARM® 2.0 GHz Cortex-A76 cores, each with 64 KB L1 I-cache, 64 KB L1 Dcache, and 256 KB L2 cache

- 4 ARM® 2.0 GHz Cortex-A55 cores, each with 32 KB L1 I-cache, 32 KB L1 Dcache, and 128 KB L2 cache

- Shared 2 MB L3 cache

- NEON multimedia processing engine with SIMDv2/VFPv4 ISA support

- DVFS technology with adaptive operating voltage from 0.55V to 0.973V

2.MD MCU subsystem

- High-performance multi-core multi-threaded processor architecture

- High-performance AXI bus interface

- Generic DMA engine and dedicated DMA channel for peripheral data transfer

- Clock-gated power management

3. External memory interface

- LPDDR4X up to 16 GB (2 lanes, 16-bit data bus width)

- Data rates up to LPDDR4X-4266Mbps

- Self-refresh/partially self-refresh mode

- Low-power operation

- Programmable slew rate of memory controller I/O pads

- Dual column storage devices

- Advanced bandwidth quorum control

4. Peripherals

- USB one port with USB3.0 host/device mode or USB2.0 OTG mode

- eMMC5.1

- UFS 2.1

- 2 UARTs for debugging and application

- 8 SPI hosts for external devices

- 4 I2Cs/6 I3Cs to control peripherals such as CMOS image sensors, LCM or FM receiver modules

-Utmost. 4 PWM channels (depending on system configuration/IO usage)

- I2S for connecting an optional external high-end audio codec |

Other

What is HBM (High Bandwidth Memory)?

2024.09.05

What is Antenna Tuner IC?

2024.09.20

What’s the Difference between LPDDR and DDR?

2024.09.25

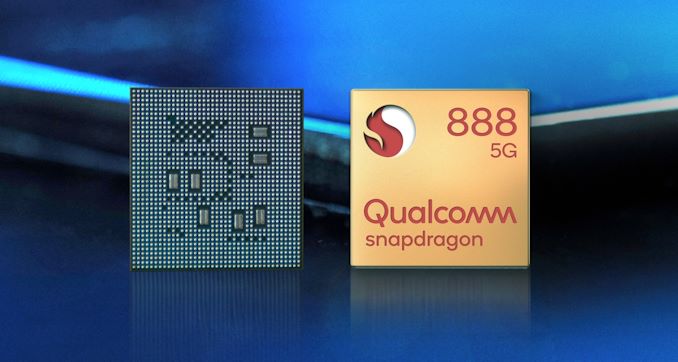

Snapdragon 888 5G Mobile Platform

2024.09.26

What is WiFi 6E?

2024.09.26

What is Bluetooth Audio SoC?

2024.09.26

What's HBM3E (High Bandwidth Memory 3)?

2024.09.26

What is an Audio Codec?

2024.10.09